# A500 Hardware Guide

Part No ???, ??? Issue No 0.0 10 November 1916 draft • not for publication INSIDE FRONT COVER

#### O Copyright Acorn Computers Limited 1986

Neither the whole nor any part of the information contained in, or the product described In, this manual may be adapted or reproduced in any material form except with the prior written permission of the copyright holder.

The product described in this manual is subject to continuous developments and improvements. All particulars of the product and its use contained in this manual are given by Acorn Computers in good faith. however, all warranties implied or expressed, including but not limited to implied warranties or merchantability or fitness for purpose, are excluded.

This manual is intended only to assist the reader in the use of the product. Acorn Computers shall not be liable for any loss or damage arising from the use of any information in this manual, or any error or omission in such information, or any incorrect use of the product.

ISBN ? ????? ??? ?

Published by: Acorn Computers Limited, Fulbourn Road, Cherry Hinton, Cambridge CB1 4JN, UK

## Contents

| I. | Introduction                                               | 2        |

|----|------------------------------------------------------------|----------|

| 2. | General Circuit Description                                | 4        |

| 3. | The Memory sytem                                           | 5        |

| 4. | The Video system                                           | 6        |

| 5. | The Sound system                                           | 7        |

|    | 5.1 The Video Controller Sound System Hardware             | 7        |

|    | 5.2 The Memory Controller Sound System Hardware            | 7        |

|    | 5.3 The I/O Controller Sound System Hardware               | 8        |

| 6. | The 1O system                                              | 9        |

|    | 6.1 Programming Model                                      | 9        |

|    | 6.2 Access Speed                                           | 9        |

|    | 6.2.1 Byte Accesses                                        | 9        |

|    | 6.2.2 Half-Word Accesses                                   | 9        |

|    | 6.2.3 Word Accesses                                        | 9        |

|    | 6.3 1O address memory mapping                              | 9        |

|    | 6.4 IOC Internal Register Map                              | 10       |

|    | 6.5 1O peripheral memory map                               | 10       |

|    | Keyboard                                                   | 14       |

|    | PCB general layout                                         | 15       |

| 9. | Detailed Hardware description                              | 17       |

|    | 9.1 Physical RAM                                           | 17       |

|    | 9.2 Video                                                  | 17       |

|    | 9.3 Sound                                                  | 17       |

|    | 9.4 Address and Read/Write Latches                         | 17       |

|    |                                                            | 9.5      |

|    | Data                                                       | 17       |

|    | 9.6 Serial line                                            | 17       |

|    | 9.7 I2C, Real Time Clock and RAM                           | 19       |

|    | 9.8 ECOnet                                                 | 19       |

|    | 9.9 Floppy Discs                                           | 20       |

|    | 9.9.1 Floppy Disc corrtroller                              | 20       |

|    | 9.9.2 Drive Powering                                       | 20       |

|    | 9.9.3 Motor Control and the Little Red Light               | 20       |

|    | 9.9.4 Eject                                                | 20       |

|    | 9.10 Winchester Discs                                      | 20       |

|    | 9.10.1 Read data recovery                                  | 20       |

|    | 9.10.2 Write data                                          | 21<br>21 |

|    | 9.10.3 Large Drives<br>9.10.4 Drive Power                  | 21       |

|    |                                                            | 21       |

|    | 9.11 Discs and RFI                                         | 21       |

|    | 9.12 Keyboard Interface<br>9.13 POR and RESET              | 21       |

|    | 9.14 Expansion Podules and Backplane                       | 22       |

|    | 9.14.1 Podule and Physical slots                           | 22       |

|    | 9.14.2 Backplane                                           | 22       |

|    | 9.15 Fan                                                   | 22       |

|    | 9.16 RFI                                                   | 23       |

| 10 | ). Programming Details                                     | 23<br>2A |

| 11 | 10.1 IOC Keyboard Asynchronous Receiver Transmitter (KART) | 24       |

|    | 10.1.1 Serial Tx Data register                             | 24       |

|    | Torra Seria IA Dula register                               |          |

A 500 Hardware Guide Issue 0.0

| 10.1.2 Serial Rx Data register                                       | 24 |

|----------------------------------------------------------------------|----|

| 10.1.3 Initialisation                                                | 24 |

| 10.1.4 Receive Interrupt                                             | 25 |

| 10.2 External Latch A                                                | 26 |

| 10.2.1 Bit [0:3] US[0:3]                                             | 26 |

| 10.2.2 Bit 4 Side Select                                             | 26 |

| 10.2.2 Bit 4 Side Select<br>10.2.3 Bit 5 Floppy Motor ON/OFF Control | 26 |

| 10.2.4 Bit 6 In Use                                                  | 26 |

| 10.2.5 Bit 7 Disc Eject                                              | 20 |

| 10.3 External Latch B                                                | 27 |

|                                                                      | 27 |

| 10.3.1 Bit [0:2] CD[0:2]<br>10.3.2 Bit 3 FDCR                        | 27 |

|                                                                      |    |

| 10.3.3 Bit 4 Printer Strobe                                          | 28 |

| 10.3.4 Bit 5 IMute                                                   | 28 |

| 10.3.5 Bit 6 OMute                                                   | 28 |

| 10.3.6 Bit 7 HS3                                                     | 28 |

| 10.4 Interrupts                                                      | 29 |

| Internal Interrupt Events                                            | 29 |

| External Interrupt Events                                            | 29 |

| Level Interrupts                                                     | 29 |

| Latched Interrupts                                                   | 29 |

| Synchronisation                                                      | 29 |

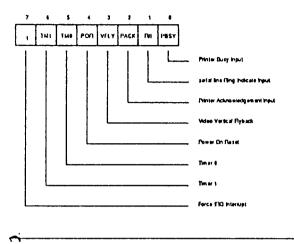

| 10.5 IRQ Status A                                                    | 29 |

| 10.5.1 Bit 0 PHSY                                                    | 30 |

| 10.5.2 Bit 1 RII                                                     | 30 |

| 10.5.3 Bit 2 Printer Acknowledge                                     | 30 |

| 10.5.4 Bit 3 Vertical flyback                                        | 30 |

| 10.5.5 Bit 4 Power-on Reset                                          | 30 |

| 10.5.6 Bit [5:6] Timer 0 and Timer 1 events                          | 30 |

| 10.5.7 Bit 7 Force                                                   | 30 |

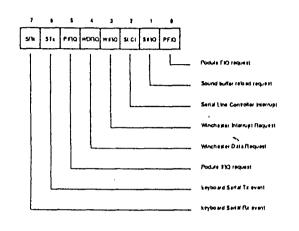

| 10.6 IRQ Status B                                                    | 31 |

| 10.6.1 Bit 0 Podule FIQ request                                      | 31 |

| 10.6.2 Bit 1 Sound buffer swap                                       | 31 |

| 10.6.3 Bit 2 Serial line controller                                  | 31 |

| 10.6.4 Bit 3 Winchester interrupt                                    | 31 |

| 10.6.5 Bit 4 Winchester data request                                 | 31 |

| 10.6.6 Bit 5 Podule interrupt request                                | 31 |

| 10.6.7 Bit 6 Keyboard transmission event                             | 32 |

| 10.6.8 Bit 7 Keyboard reception event                                | 32 |

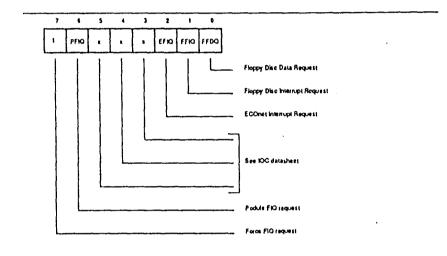

| 10.7 Interrupt Status FIQ                                            | 32 |

| 10.7.1 Bit 0 Floppy disc data request                                | 32 |

| 10.7.2 Bit 1 Floppy disc interrupt request                           | 32 |

| 10.7.3 Bit 2 ECOnet interrupt request                                | 32 |

| 10.7.4 Bit [3:5] Undefined                                           | 32 |

| 10.7.5 Bit 6 Podule FIQ request                                      | 33 |

| 10.7.6 Bit 7 Force                                                   | 33 |

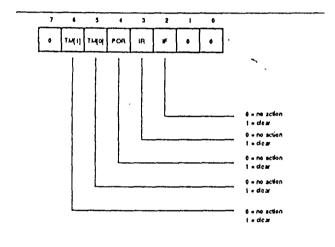

| 10.8 IRQ Clear register                                              | 33 |

| 10.9 Interrupt Request registers 3200014H 3200024H 3200034H read     | 33 |

| 10.10 Interrupt Mask registers 3200018H 3200028H 3200038H read/write | 34 |

| 10.11 Control Port                                                   | 35 |

| 10.11.1 C[0:1] The 12C Bus                                           | 35 |

| 10.11.2 Control port read                                            | 35 |

| 10.11.3 Control port write                                           | 35 |

|                                                                      |    |

.A 500 Hardware Guide Issue 0.0

v

| 10.12 Counters                                   | 36 |

|--------------------------------------------------|----|

| 10.12.1 Register actions                         | 36 |

| 10.12.2 Counter schematic                        | 36 |

| 10.12.3 Counter Registers                        | 37 |

| 10.12.4 Counters 0 and 1                         | 37 |

| 10.12.5 Counter 2 (BAUD))                        | 37 |

| 10.12.6 Counter 3 (KART)                         | 38 |

| 11. Reset and Power-on                           | 39 |

| 12. Mechanical                                   | 41 |

| 12.1 Construction                                | 41 |

|                                                  | 41 |

| 12.2 Installing Podules<br>12.3 The Disc Tray    | 41 |

|                                                  | 41 |

| 12.4 Removing the Main PCB                       |    |

| 12.5 Changing the Batteries                      | 41 |

| 12.6 Changing the ROM's                          | 41 |

| 12.7 Air flow                                    | 41 |

| 13. Main PCB Connectors, Links and Test Points   | 42 |

| 13.1 TPI HLD Head Load                           | 43 |

| 13.2 TP2-TP5 Guard rail                          | 43 |

| 13.3 SKI Audio Output                            | 43 |

| 13.4 SK2 RGB Video output                        | 43 |

| 13.5 SK3 Monochrome video output                 | 44 |

| 13.6 SK4 RS423 Serial line                       | 44 |

| 13.7 SK5 Parallel printer connector              | 44 |

| 13.8 SK6 Podule backplane expansion              | 45 |

| 13.9 SK7 Floppy disc drive connector             | 46 |

| 13.10 SK8 and SK9 Winchester data connector      | 46 |

| 13.11 SK10 Winchester control connector          | 47 |

| 13.12 SK11 Keyboard connector                    | 47 |

| 13.13 SK12 and SK13 Power connectors             | 48 |

| 13.14 SK14 ECOnet connector                      | 48 |

| 13.15 LK1 20/24MHz Clock option                  | 49 |

| 13.16 LK2 ROM expansion                          | 49 |

| 13.17 LK3 and LK4 1M/256k RAM option             | 49 |

| 13.18 LK5 3/2u ARM option                        | 49 |

| 13.19 LK6 and LK7 ROM size option                | 49 |

| 13.20 LK8 Monochrome video option                | 49 |

| 13.21 I.K9 VIDC speed select                     | 49 |

| 13.22 LK10 Monochrome video option               | 49 |

| 13.23 LK 11 Unused IOC input                     | 50 |

| 13.24 LK12 FDC power option                      | 50 |

| 13.25 LK13 FDC ready option                      | 50 |

| 13.26 LK14 and LK15 Floppy Drive power option    | 50 |

| 13.27 LK16 Winchester write-precomp option       | 50 |

| 13.28 LK16 and LK17 Winchester RWC or HS3 option | 50 |

| 13.29 LK18 Speaker                               | 50 |

| 13.30 LK19 RTC frequency TEST                    | 51 |

| 13.31 IC10 Video header                          | 51 |

| 13.32 Power Connections                          | 51 |

| 14. A500 Parts List                              | 52 |

| 14.1 Main PCB                                    | 52 |

| 14.1.1 Integrated Circuits                       | 52 |

| 14.1.2 Capacitors                                | 53 |

|                                                  |    |

| 14.1.3 Resistors                               | 53 |

|------------------------------------------------|----|

| 14.1.4 Diodes                                  | 54 |

| 14.1.5 Transistors                             | 54 |

| 14.1.6 Misc                                    | 54 |

| 14.1.7 Connectors                              | 55 |

| 14.1.8 IC Sockets                              | 55 |

| 14.1.9 Links                                   | 55 |

| 14.2 PSU                                       | 56 |

| 14.3 Disc Sub-System                           | 56 |

| 14.3.1 Floppy Disc                             | 56 |

| 14.3.2 Winchester Disc                         | 56 |

| 14.3.3 Batterys                                | 56 |

| 14.4 Fan                                       | 56 |

| 15. Modifications                              | 57 |

| 16. Appendix A Keyboard Protocol               | 58 |

| 17. Appendix B The A500 Keyboard               | 60 |

| 17.1 Keyboard Hardware Description             | 60 |

| 17.2 6500/11 Port Map                          | 60 |

| 17.3 Notes                                     | 60 |

| 17.4 Key Matrix to Key Number                  | 61 |

| 17.5 Keyboard Links Connectors and Test Points | 62 |

| 17.6 Keyboard connector (PL4):                 | 62 |

| 17.6.1 Pins 1 and 3: Data                      | 62 |

| 17.6.2 Pin 2: Reset.                           | 63 |

| 17.6.3 Pin 4: Power                            | 63 |

| 17.6.4 Pin 5: Audio                            | 63 |

| 17.6.5 Pin 6: Power                            | 63 |

| 17.6.6 Pin 7: Power                            | 63 |

| 17.7 Mouse connector (PL1):                    | 63 |

| 17.8 SPD1 connector (PL2):                     | 63 |

| 17.9 Keyboard PCB Parts                        | 64 |

| 17.9.1 Integrated Circuits                     | 64 |

| 17.9.2 Resistors                               | 64 |

| 17.9.3 Diodes                                  | 64 |

| 17.9.4 Crystals                                | 64 |

| 17.9.5 Capacitors                              | 64 |

| 17.9.6 Sockets                                 | 65 |

| 17.9.7 Misc                                    | 65 |

| 18. Appendix C Key Number to Legend            | 66 |

| 19. Appendix D Podules                         | 68 |

| 19.1 Device Drivers and the Podule Manager     | 68 |

| 19.2 Simple Podules                            | 68 |

| 19.3 Memc Podules                              | 68 |

| 19.4 Co-Processor Podules                      | 68 |

| 19.5 Software Requirements                     | 68 |

| 19.6 Hardware Requirements                     | 68 |

| 19.7 Podule Identification                     | 68 |

| 19.7.1 Identification Extension                | 68 |

| 19.8 Podule Presence                           | 69 |

| 19.9 Interrupts                                | 69 |

| 19.9.1 Podule IRQ                              | 69 |

| 19.10 Examples                                 | 69 |

| 19.10.1 Minimum Identification                 | 69 |

A500 Hardware Guide Issue 0.0

vii

19.10.2 Simple Podule Example 19.11 Signal Explanations

A500

## 1. Introduction

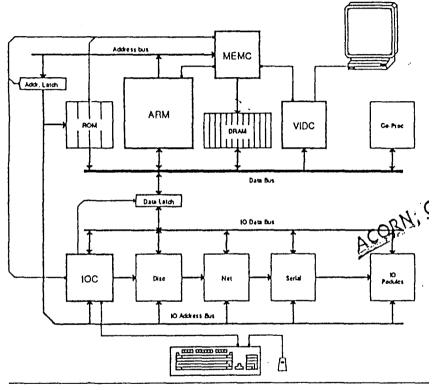

The A500 is a high performance personal workstation intended for software development of future Acorn products. It is built around four fully custom VLSI devices. These are the A Series chip set, which comprise the Acorn Risc Machine (ARM), Memory Controller (MEMC), Video Controller (VIDC) and Input Output Controller (IOC). With the addition of a number of peripheral chips. a Case, a PSU, a detachable keyboard and a CRT the A Series chip set is the basis of a flexible computing engine.

See ARM,MEMC,VIDC and IOC datasheets for additional information on the A series chip set.

#### FEATURES

- 8 MIPS peak

- 4 MByte RAM

- 1/4 MByte ROM

- Virtual Memory support

- 95 key keyboard with speaker and mouse

- 1.6 MByte floppy disk

- 20 MByte winchester disk

- Parallel printer interface

- ECOnet interface

- RS423 serial interface

- Four internal IO expansion slots

- Battery backed-up Real Time Clock and 256 Bytes of RAM

- Linear RGB output

- Composite video output

- · High quality stereo sound output

- 1152 x 864 at 1 bit per pixel 60 Hz refresh

- 640 x 480 at 4 hits per pixel 60 He refresh

- 640 x 256 at 8 bits per pixel 50 Hz refresh

Figure 1: A500

## 2. General Circuit Description

The ARM is a low cost, pipelined 32 bit reduced instruction set processor with very low interrupt latency. It accepts instructions and manipulates data via a high speed 32 bit data bus and 26 bit address bus. All instructions are restartable allowing true virtual mcmory support.

The Memory Controller (MEMC) acts as the interface between the ARM and the rest of the *A Series* chip set, Read-Only memories (ROM), and Dynamic memory devices (DRAM), providing all the critical system timing signals.

Up to 4MBytes of DRAM may be connected to MEMC, which provides all signals and refresh operations for a wide variety of standard DRAMs. A *Logical to Physical Address Translator* maps the Physical Memory into a 32MByte Logical address space (with three levels of protection) allowing Virtual Memory and Multi-Tasking operations to be implemented. Fast "page mode" DRAM accesses are used to maximise memory bandwidth. The. VIDC requests data from the RAM when required, and buffers it in one of three FIFOs before using it. Data is requested in blocks of four 32-bit words, allowing efficient use of paged-mode DRAM without locking up the system data bus for long periods.

MEMC supports Direct Memory Access (DMA) read operations with a set of programmable DMA Address Generators, which provide a circular buffer for Video data, a linear buffer for Cursor data, and a double buffer for Sound data.

The Video Controller (VIDC) takes video data from the video FIFO, serialises it and passes it through a colour look-up palette, and converts it to analogue signals for driving the CRT guns. The chip also controls all the display timing parameters and controls the position and pattern of the cursor sprite. In addition, the VIDC incorporates an exponential Digital to Analog Converter (DAC) and stereo image table for the generation of high quality sound from data in the DRAM.

The VIDC is a highly programmable device, offering a very wide choice of display formats. The pixel rate can be selected between 8 and 24MHz and the data can be serialised to either 8, 4, 2, or 1 bit per pixel. The horizontal timing parameters can be controlled to units of 2 pixels, and the vertical timing parameters can be controlled to units of a raster. The colour look-up palette which drives the three on-chip DACs is 13 bits wide, offering a choice from 4096 colours or an external video source.

The cursor sprite is 32 pixels wide, and any number of rasters high. Three simultaneous colours (again from a choice of 4096) arc supported, and any pixel can be defined as transparent, making possible cursors of many shapes. It can be positioned anywhere on the screen. The sound system implemented on the device can support up to 8 channels, each with a separate stereo position.

## 3. The Memory sytem

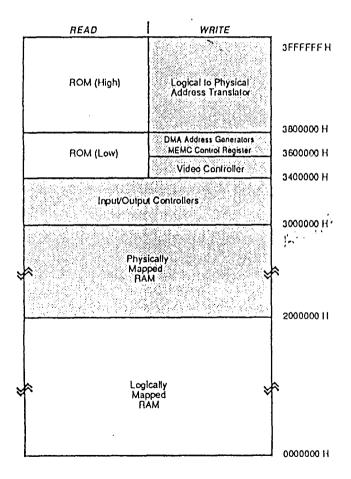

All data is manipulated through internal registers, memory or the co-processor interface which is only supported by the 2  $\mu$  ARM. The memory consists of physical ram and memory mapped devices. These devices are the programming registers of the MEMC, VIDC. IOC and the IO peripherals. The partitioning of the memory space is shown in figure 2. The shadded areas are accessible only when the ARM is in supervisor mode.

A 500 Hardware Guide Issue 0.0

## 4. The Video system

The VIDC is reponsible for all the system display functions and only a minimal amount of off-chip line driving is required to drive a standard monitor, which may be monochrome or colour, and may support PAL broadcast standard timings or, for higher resolutions, a 32 kHz line rate.

The A500 also supports a 1152\*864 resolution monochrome mode, which exploits the VIDC external high-resolution shifter to give a 96 MHz pixel rate. A suitable monitor for this display mode would have a 60 kHz line rate.

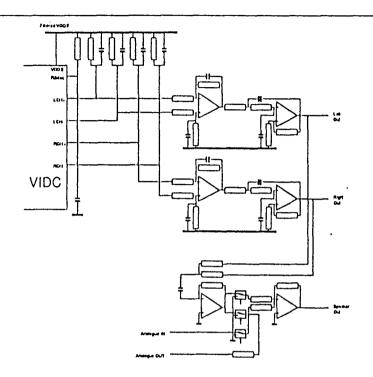

## 5. The Sound system

The sound system is based on the VIDC stero sound hardware, External analogue anti-alias filters are used which are optimised for a 20 kHz sample rate. The high quality sound output is available at a 3.5mm stero jack socket at the rear of the machine which will directly drive personal stereo headphones or alternately an amplifier and speakers. A mono mix of the sound output is sent to the keyboard loudspeaker. In addition various mixing and muting functions are provided.

## 5.1 The Video Controller Sound System Hardware

VIDC contains an independent sound channel consisting of the following components. A four-word FIFO buffers sixteen 8-bit sound samples with a DMA request issued whenever the last byte is consumed from the FIFO. The sample bytes are read out at a constant sample rate programmed into the 8-bit Audio Frequency Register; this may be programmed to allow samples to be synchronously output at any integer value between 3 and 255 microsecond intervals (with an 24MHz VIDC clock).

The sample data bytes are treated as sign plus seven-bit logarithmic magnitude and after exponential digital to analogue conversion, de-glitching and sign-bit steering are output as a current at one of the audio output pins to be integrated and filtered externally.

VIDC also contains a bank of eight stereo image position registers each of 3 bits. These 8 registers are sequenced through at the sample rate with the first register synchronised to the first byte clocked out of the FIFO. Every sample time is divided into eight time slots and the three bit image value programmed for each register is used to pulse width modulate the output amplitude between the LEFT and RIGHT audio current outputs in multiples of time slot subdivisions. This allows the signal to be spatially positioned in one of seven stereo image positions. (The first period of every sample is muted internally to absorb any DAC output current glitches).

For further information refer to the VIDC data sheet.

## 5.2 The Memory Controller Sound System Hardware

MEMC provides three internal DMA address registers to support Sound buffer output; these control the DMA operations performed following Sound DMA requests from VIDC. The registers allow the physical addresses for the START, PNTR (incremental) and END buffer pointers to a block of data samples in the lowest half Megabyte of physical RAM to be accessed and operate as follows: programming a 19-bit address into the PNTR register sets the physical address from which sequential DMA reads will occur (in multiples of 4 words) and programming the END pointer sets the last physical address of the buffer. Whenever the PNTR register increments up to this END value the address programmed into the START register is automatically written into the PNTR register for the DMA to continue with a new sample buffer in memory. A Sound Buffer Interrupt (IRQ) signal is generated when the reload operation occurs which is. processed by IOC as a maskable interrupt (IRQ) source.

The Memory Controller also includes a sound channel enable signal which is necessary in order to disable the sound DMA acknowledgments to the Video Controller when the sound output is to be suppressed. Because this enable/disable control signal is not synchronised to the sound sampling requests one would normally only disable requests after the waveforms being synthesised have been programmed to decay to zero amplitude; the last value loaded into the Audio data latch in the VIDC will in fact be output to each of the Stereo image positions at the current Audio Sample rate.

There are several important constraints which must be observed when programming the Sound DMA Buffer addresses. Firstly, because a 4-word FIFO is provided in VIDC, buffer lengths are constrained to multiples

#### Chapter 3

of four words: although 17 bits in the address registers are programmable, the two low-order bits are ignored. Secondly, the END condition test is in fact a test for equivalence rather than 'greater-than-or-equal', with the result that the END address must be programmed to an address greater than the (dynamically incrementing) PNTR register. In addition, as soon as a Buffer finished signal interrupt is detected then the new END value must be programmed because the PNTR register is now advancing from the reloaded START address - interrupt acknowledge latencies may well become critical with high sample frequencies and short DMA buffers.

The provision of the three registers is in fact well suited to both single and multiple DMA buffer systems. In the case of a simple waveshape that is to be repeatedly output then the START and END registers can be left programmed to point to the physical buffer addresses and the PNTR address will automatically loop round with no further action required. With two or more buffer operation the reprogramming of the END of the current buffer and the START of the next buffer are the only critical operations and should be performed together as soon as possible after a hardware buffer pointer switch interrupt has occurred.

## 5.3 The I/O Controller Sound System Hardware

IOC provides three programmed output control signals which are to turn on or off external analogue switches in order to provide routing of the audio signals, as well as an interrupt enable/status/reset register interface for the Sound Start Buffer reload signal generated by the Memory Controller.

Bit 1 in the Interrupt High Register bank has been allocated in IOC and the interrupt may be enabled by setting this bit in the INTmask High register, monitored directly in the INTstatus High register and masked with the current enable mask in the INTrequest High register, and cleared by writing to this bit in the INTclear register.

The three audio routing control lines are defined as OMUTE which disables sound output from the Podule Analogue Output bus, PMUTE which disables external Podule Analogue Input signals being mixed with the internal sound source, and SMUTE which mutes all output to the internal loudspeaker situated in the keyboard. The OMUTE and PMUTE reflect the status of bits 14 and 13 respectively of the programmable (write-only) External Register (which are uninitialsed at power up) and SMUTE which reflects the state of Bit 5 of the Control port of IOC (the Internal speaker is muted at power up).

The stereo output to the Hi-Fi stereo output is in fact not mutable with SMUTE and always reflects the current output of the DAC channels.

A 500 Hardware Guide Issue 0.0

## 6. The IO system

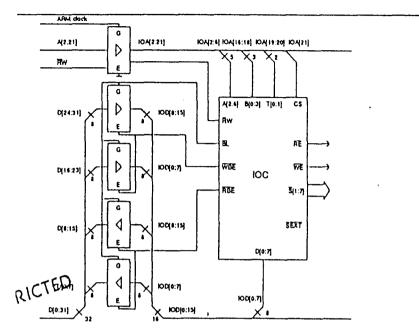

The IO system is controlled by the IO Controller IOC and the Memory Controller MEMC. It has a 16 bit Data interface which could be expanded to 32 bits or shrunk to 8 bits on future A Series products. The IO Bus supports all the internal peripherals and the PODULE expansions.

## 6.1 Programming Model

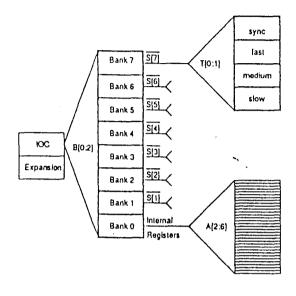

The Bank B[0:2], Type T[0:1], Chip Select CS and Addresses Lines A[2:6] of IOC are joined to the CPU address lines and the IOC and peripherals are viewed as memory mapped devices. This allows the programmer to specify in a single memory instruction the peripheral to be accessed and the type of timing cycle it requires. As shown in figure 2 the IO Controller space is divided into two halves. The upper half is occupied by IOC, and the lower half is left for additional IO Controllers.

The IOC space is decoded into eight banks, bank zero through seven, by the B[0:2] lines. The bottom bank, bank zero, maps to the internal registers of IOC. The remaining seven banks map to the seven peripheral select lines S[1:7] respectively. The seven peripheral banks are each further decoded into four types of peripheral access by the T[0:1] lines. (See figure 2.) The type of the peripheral access determines the timing of the data transfer cycle.

A particular peripheral device may be accessed by choosing an address where CS is HIGH, B[0:2] decodes to the appropriate peripheral select, and T[1:0] selects a cycle with timing to suit the accessed device. The remaining low order address lines may be used to select the register within the device.

## 6.2 Access Speed

While the peripherals appear as memory mapped devices, it is not possible for accesses to them to be completed in the same time as accesses to main memory. Four different access cycle timings are available and the timing for an access is determined from the state of T[0:1] at the start of the access.

### 6.2.1 Byte Accesses

To access byte wide peripherals byte instructions should be used. A byte store operation will place the written byte on all four bytes of the word and will therefore correctly place the desired value on the lowest byte of the IO Bus. A byte or word load may be used to read a byte wide peripheral into the lowest byte of an ARM register.

### 6.2.2 Half-Word Accesses

To access half-word peripherals word instructions should be used. When storing, The half-word must be placed on the upper 16 bits, D[16:31]. To maintain upwards compatibility half-word stores should replicate the written data on both half-words. When loading, the upper sixteen bits are undefined.

### 6.2.3 Word Accesses

These are not supported on the A500.

### 6.3 10 address memory mapping

The IOC is connected as detailed in table 1.

A 500 Hardware Guide Issue 00

Figure 2: A 500 IO system

## 6.4 IOC Internal Register Mal)

All internal registers are accessed with no wait states, and accesses take two REF8M cycles to complete. The internal registers are decoded as bank zero, so to access them the B[0:2] lines must all be LOW and the IOC must be selected by taking CS HIGH. The individual registers are then addressed using the A[2:6] lines. The registers are decoded on word boundaries. The state of the T[0:1] lines is ignored. The address are shown in table 2 below.

## 6.5 I0 peripheral memory map

The IO devices in the A500 are accessed using the addresses shown in table 3 below. External podules should only be used at the slowest speed to allow for external buffer delays.

Figure 3: Decoding Structure

| 100    |   | ARH     |

|--------|---|---------|

|        |   |         |

| [OE]   | - | [A[21]] |

| [T[1]] | - | [\{20}] |

| {T[0]] | - | [A[19]] |

| [8[2]] | - | [A{18]] |

| [B[]]] | - | [A[17]] |

| [B[0]] | - | [A[16]] |

Table 1: IOC address mapping

| <br>  Address                                                                                                                                                                                                                                                                                                                                                                                      | l<br>Read<br>I                                                                                                                                                                                           | Nrite I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3200000H           320000H           320000H           320000H           320000H           320000H           320000H           320000H           320000H           320000H           320001H           320001H           320001H           320001H           320002H           320002H           320002H           320002H           320002H           320002H           320002H           320002H | Read<br>Control<br>Serial Rx Data<br>-<br>IRQ status A<br>IRQ request A<br>IRQ mask A<br>-<br>IRQ status B<br>IRQ mask B<br>-<br>IRQ mask B<br>-<br>FIQ status<br>FIQ request<br>FIQ request<br>FIQ mask | Write<br>Control<br>Serial Tx Data<br>-<br>-<br>IRQ cloar<br>IRQ mask A<br>-<br>IRQ mask B<br>-<br>-<br>FIQ mask                                                                                                                                                                                                                                                                                                                                                                                  |

| <pre>1 3200044H 1 3200048H 1 320004CH 1 3200050H 1 3200054H 1 3200058H 1 320005CH 1 320005CH</pre>                                                                                                                                                                                                                                                                                                 | TO count Low<br>TO count High<br>-<br>TI count Low<br>TI count Low<br>TI count High<br>-<br>T2 count Low<br>T2 count High<br>-<br>T3 count Low<br>T3 count High<br>-                                     | -         1 T0 latch Low         1 T0 latch High         1 T0 latch command         1 T0 latch command         1 T1 latch Low         1 T1 latch High         1 T1 latch command         1 T1 latch Kigh         1 T1 latch command         1 T1 latch High         1 T1 latch command         1 T2 latch High         1 T2 latch Command         1 T2 latch Command         1 T2 latch High         1 T2 latch Low         1 T3 latch High         1 T3 latch command         1 T3 latch command |

Table 2: Internal register memory map

| Cycle  <br>Type Bank | Base  <br>Address | tc I     | Use                          |  |  |  |  |  |

|----------------------|-------------------|----------|------------------------------|--|--|--|--|--|

| Fest 1   \$3310000   |                   | 9793     | <br>  Floppy Disc Controlier |  |  |  |  |  |

| Sync 2 4             | 43340000          | 6854     | ECOnet Controller            |  |  |  |  |  |

| Sync 3               | 63380000          | 6551     | Serial Line Controller       |  |  |  |  |  |

| \$10w 4              | 43240000 1        | Podule I | Internal Podules             |  |  |  |  |  |

| Hed. 4               | 4320000 1         | Podule   | Internal Podules             |  |  |  |  |  |

| Fast 4               | 63340000 1        | Podule i | Internal Podules             |  |  |  |  |  |

| Sync 4               | 63300000          | Podule   | Internal Podules             |  |  |  |  |  |

| 1                    | 1                 | t        |                              |  |  |  |  |  |

| Mad. 5               | #35D0000          | 11D63463 | Winchester REGISTER WRITE    |  |  |  |  |  |

| Med. 5               | \$32D0020         | 11D63463 | Winchester REGISTER READ     |  |  |  |  |  |

| Med. 5               | 432D0008          | HD63463  | Winchester DMA READ          |  |  |  |  |  |

| Med. 5               | 432D0028          | HD63463  | Winchester DMA WRITE         |  |  |  |  |  |

| Fast 5               | 63350010 1        | HC574    | Printer Data                 |  |  |  |  |  |

| Fast 5               | 43350018          | HC574    | Latch B                      |  |  |  |  |  |

| Fast 6               | 63360000 1        | HC574    | Latch A                      |  |  |  |  |  |

| Slow 7               | £3270000          | Podule   | External Podules             |  |  |  |  |  |

Table 3 Peripheral Addresses

## 7. Keyboard

The keyboard is a seperately housed unit which communcates with the main processor box via a duplex serial link. At the keyboard end the serial link is controlled by a 6500/11 microcontroller, and at the processor end by the IOC keyboard interface. The link is designed to support a number of different keyboards but it is hopped that only one will be necesary. The keyboard is powered via the serial link and the mono audio output is made available. The keyboard may also reset the main processor but keyboard should be designed so that plugging and unplugging them from the main processor does not cause a reset to occure.

The keyboard is responsible fur detecting keys states, tracking mouse movement, and sending data through the SPD (software protection device) for encription.

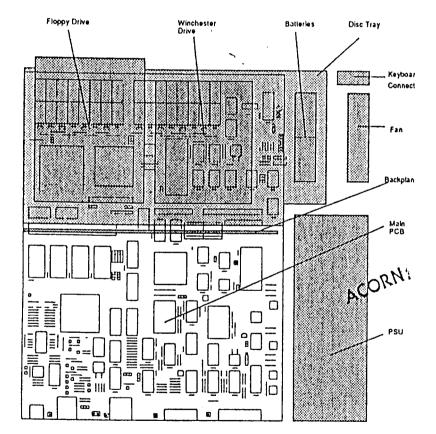

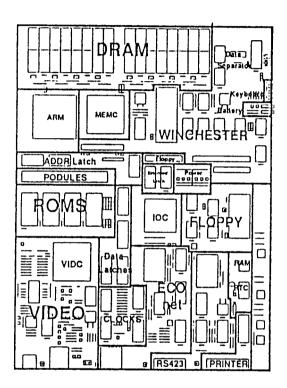

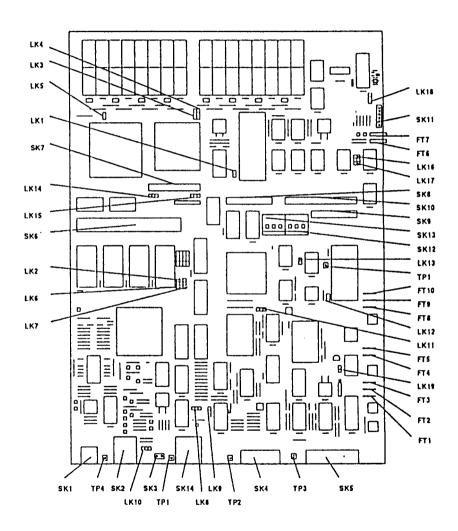

# 8. PCB general layout

A 500 Hardware Guide Issue 0.0 15

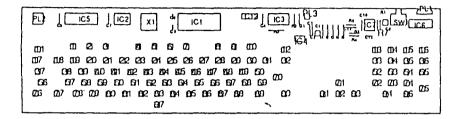

Figure 4: A 500 main PCB

A 500 Hardware Guide Issue 0.0

## 9. Detailed Hardware description

## 9.1 Physical RAM

The physical RAM consists of 32 1 MBit DRAMs. With the 8 MHz ARM the access speed must be 120 nS or better. The RAM Dout pins have series restistor (R??? to R???) to limit the slew rate and prevent undershoot. The CAS line is negated before the processor has latched data on a read cycle. The system relies on dynamic storage on the data bus to operate. It is important that all the loads on the data bus are CMOS-

## 9.2 Video

The A500 uses the VIDC custom chip. This is not compatible with VIDC2 a very similar chip which replaces VIDC. The programming differences are confined to the sound system but the video output drivers have been redesigned.

## 9.3 Sound

## 9.4 Address and Read/Write Latches

The pipelined ARM addresses and NOTread/write line are latched by IC35,IC36 and IC37 to provide valid signals thoughout both IO and ROM accesses. The latches arc controlled by the PHI2bar clock line which is stretched low during slow cycles.

## 9.5 Data

The ARM data but it connected to the IO data bus by a set of latches IC17,IC18,IC28,IC29. These provide two functions. Firstly they isolate the IO bus load from the main data bus and secondly they allow for the mis-match in speed between the two busses. These buffers are controlled by the BL, RBE and WBE lines from IOC. The BL line may also be driven from the backplane by an open-drain driver. When undriven the latches must remain transparent and BL is pulled high by RP1/2 and R44. The rise time of this signal must be fast enough to allow consecutive IO cycles, the limit is the output low current of BL of 10mA. The organisation of the latches is slightly unusual and is done to minimise the capacitive loading on the main memory bus.

## 9.6 Serial Line

The serial line is both RS232 and RS423 compatible with a typical input impedence of 5K ohms. All inputs have a 100mV offset for off-line detection. The controller is a RockweB 65C51 IC21. It has a single baud rate generator derived from its own crystal. Split baud rates are obtained by using the programmable BAUD output from IOC. The series resister R81 is needed as on reset 1C21/5 becomes an ouytput and clashes with BAUD . To allow external modems to be used the serial interface connector provides a *Ring Indicate* input which may generate an interrupt. To enable the serial interface CTS, DCD and DSR must be active. This can be achieved by connecting them to the DTR output.

Figure 5: Sound Hardware

A 500 Hardware Guide Issue 0.0

## 9.7 I2C, Real Time Clock and RAM

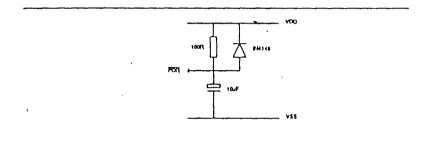

A Real Time Clock (RTC), 1C22 and 256 bytes of CMOS RAM, 1C23 arc provided on an I2C serial bus. Data is maintained while the mains power to the machine is switched off by two dry cells. They may be replaced while the macine is switched on without loss of data. D11 and D12 "mix" the computer and battery rails. C29 protects Vd as the machine is switched on and off. The lowest battery voltage less the voltage drop across D11 must be greater than 1.1 volts. The RTC can detect if both the mains and battery power have failed. The RAM contents should be protected with a software checksum. The RTC chip only provides a readable output pin toggled every second for fine resolution. Care must be taken to ensure monotonic time is returned to the user. (Future machines may use a combined RTC and RAM chip, PCF8583, which is currently unavailable but solves this problem). The RTC reference crystal X3 needs tuning by C45 we do not know how critical this will be in production. RP2/8 and TR13 help minimise the power consumption. The open-drain I2C bus is pulled up by RP2/4,5. Note : the pull-ups are a diode drop above Vdd. The estimated power consumption is 50uA giving a five year battery life.

## 9.8 ECOnet

The clock detection circuit uses half a 74LS123, IC20. An incoming clock pulse triggers the monostable which has a time constant of approximately 20µs (2n2 and 39k C21,R59) thus generating a "Data Carrier Detect". If a subsequent pulse is not detected within 20µs the "Data Carrier Detect" signal is removed-

The chatter disconnect circuit uses half an 74LS123, IC20. This ensures that the transmitter does not hold the line for an unreasonable time thus jamming the network. This can only happen in error if the computer malfunctions. When a transmission is started "Request to Send" is asserted and the monostable triggered thus enabling the line driver, IC5. When the transmission finishes RTS is deasserted and the driver disabled. However should the monostable time out before this the driver is again disabled. The time constant of the monostable is approximately 4.5seconds (100uP and 100k C22,R60). This value is calculated as follows.

The use of a 74LS123 NOT a 74HC123 is important as the trigger to output delay it much larger with the HC device.

slowest network 50E3 bits per second

| largest packet   | = | 20E3 bytes                          |

|------------------|---|-------------------------------------|

|                  | = | 160E3 bits                          |

|                  | = | 200E3 bits after protocol overheads |

| time to transmit | = | 200E3 / 50E3 seconds<br>4 seconds   |

The Collision Detect circuit consists of two comparators, one for each of the DATA+ and DATA- anti-phase signals from the network. Comparisons (against the average of the two signals, plus a small offset) are only made against the active high period of each signal. In this way, even if the two signals have a high common mode offset both comparators will be switched off and CTS will be be de-asserted. As the data lines simultaneously go through high-low or low-high transitions, the comparators will indicate a transitory fault. An RC filter R71,C24 is used to remove these glitches. Its time constant is long enough to prevent false indication, but not long enough to completely mask the data bit following a transition.

#### Chapter 9

## 9.9 Floppy Discs

The floppy disc interface will support up to four drives. The interface is useable with TTL and CMOS drives which may be  $8^{\circ}$ , 5 1/4" or 3 1/2". The behaviour of drives has changed over time and a number of links arc provided to try and cope with this. The test point TP1 makes the controller *Head Load* signal available and the link LK7 allows the *READY* input to be disabled. The resistor-pack RP3 may need changing to match drive requirements. IC33 inverts the control lines as needed full buffering of this interface is not provided as it only drives internal discs on a short ribbon cable.

### 9.9.1 Floppy Disc controller

Either the FDC9793 or FDC1793, IC34, may be fitted. If the FDC1793 is used then LK12 must be made and C49 fitted. The data seperator IC32 is an external FDC9216B. This is digital and requires no adjustment, and allows software selection of the floppy disc data rates. IC4, IC15 and IC49 generate a software programable 1 or 2 MHz square wave for the floppy controller IC34. The floppy disc controller reset line is programmed independently of the system reset by *latchB* IC39.

#### 9.9.2 Drive Powering

The floppy drive may be powered in one of two ways, either by a separate power connector or via the 34 way data cable SK7.

If conventional drives with seperate power connectors are used LK14 and LK15 should be changed.

### 9.9.3 Motor Control and the Little Red Light

The variations in specs are large. Beware.

#### 9.9.4 Eject

The preferred eject is computer controlled so that the disc may not be removed until its state is guaranteed to be consistent.

## 9.10 Winchester Discs

The winchester disc interface will support up to two ST506 winchester drives. The control interface SK10 is daisy chained between drives. There is a separate data interface SK8 and SK9 for drives 0 and 1 respectively.

The control functions are all provided by a Hitachi HD63463 HDC. This contains all of the head control, data recovery, formatting, error correction/detection, MFM conversion, parallel/serial conversion and write precompensation facilities necessary to operate a Winchester hard disc. The data synchronisation and write precompensation timing is done by a National Semiconductor DP8465N-4 and associated chips.

### 9.10.1 Read data recovery

An analogue phase locked loop tuned to a nominal 5MHz data rate is fitted. The bandwidth allows for a +/- 1% speed variation of the media. The pll operates in two modes: A capture mode, where it is a frequency loop in which it attempts to lock onto the data's fundamental frequency. If it succeeds, it then waits until two bytes of zeros or ones have been recovered from the disc and issues a signal to permit the data to flow into the HD63463. This will prevent the HDC from being fed with a data stream that may include a write splice glitch causing it to abort the access. After a further two bytes, the HDC will indicate that it is following the bit stream and issue a SYNC signal to the pll, switching it from a frequency loop to a phase only loop. The operating frequency is now constant until the end of the data block and only small phase changes are permissible in order to track the variable frequency bit stream.

A 500 hardware Guide Issue 0-0

Whilst locking, the pll's damping factor is about 1.15 and this gives it a typical locking distance of about two bytes. When locked, the damping factor falls to about 0.5 at 2-5MHz with a bandwidth of only some 30K rad/s.

When reading has stopped, the pll locks onto the 10MHz reference crystal so that a subsequent read operation finds the pll only 1% distant from its final locked on frequency.

The read data buffer IC49 is enabled by IC54/15, "lock detect", not "wgate" to prevent the controller attempting to detect sync bytes before the pll has locked. While the pll is locking R116 keeps read data low.

The read data path through the line receiver IC51 and the drive demultiplexer IC46 is inverting which is compensated for by connecting recieve + data to the inverting input.

#### 9.10.2 Write data

Write precompensation is provided by a delay line of 10ns per tap. The appropriate tap is selected by the HDC Early/Late outputs. Nominal timing is obtained when neither of these are asserted. Write precompensation may be disabled by appropriate programming of the HDC. The write pre comp circuit may be bypassed by changing link LK16. MFM conversion is done by the HDC.

During writing, the pll locks onto the 10MHz reference crystal but the write data frequency is obviously determined by the HDC's connection to this same reference and not by the pll's connection to it.

The demultiplexing of EARLY/RGATE was found to be unnecessary and has been removed.

#### 9.10.3 Large Drives

To allow drives with more than 8 heads to be used, the *reduced write current* pin of the ST506 interface may be reassigned as HS3. This is then controlled by *latchB*.

#### 9.10.4 Drive Power

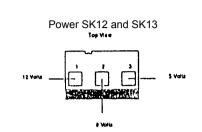

Power is available on SK12 and SK13. The current power supply, the Master 128 PSU, is capable of running ONE low power 3 1/2" winchester. Because of the vicious demands of the drive the ports should be filtered to prevent noise injection to the main board.

### 9.11 Discs and RFI

The winchester drive generates a large amount of RFI with can interfere with the floppy disc drive. Care must be taken to provide adequate shielding.

## 9.12 Keyboard Interface

The IOC pins are protected by the inverting buffers in IC31 R95 erasure that the line idles LOW so that start bits are not detected if the keyboard is disconnected. R96 protects IC31 and R97 and C48 limit the slew rate and RFI. The 12volt output is not decoupled and should be. R98 ensures the machine is not reset when the keyboard is disconnected. R99 protects IC48 and C31 ensures that charge sharing does not cause the machine to be reset when a keyboard is connected. It has been suggested that C31 might be moved to the other side of R99 to protect an external switch.

#### Chapter 9

## 9.13 POR and RESET

The internal reset signal RST may be driven either by a external source via the keyboard interface, pin 2 active LOW, or by the IOC. All sources are therefore open-drain and pulled high by RP2/8. R94 and C30 determin the length of the power-on reset pulse, this is order 1 second. This needs to be long enough to pass the power surge of the winchester. D12 trys to discharge C30 if the power fails for a short time to ensure a full width reset pulse.

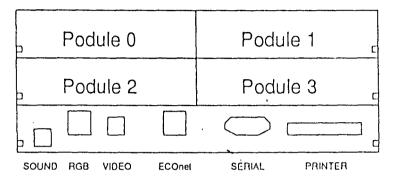

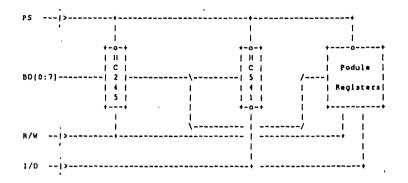

## 9.14 Expansion Podules and Backplane

All expansion for the A500 is by way of PODULES-.Every podule occupies at least one physical slot. All PODULES must obey the minimum attachment rules to allow correct mapping between PODULES, PHYSICAL SLOTS, and DEVICE DRIVERS. There are currently three classes of PODULES Simple Podules, MEMC podules and Co-processors. The backplane decodes the podule space into four podules and four MEMC: podules, using address lines LA[14:15]. Podules should be designed to be address independent and have a unique ID which allows the podule manager to bind drivers to physical addresses. However some early podule drivers are address specific and these podules must be located in the correct physical slot. R112 ensures that the podule id of a non-existent podule is read HIGH that not present.

#### 9.14.1 Podule and Physical slots

There are four internal podule slots in the A500. A standard podule occupies a single podule slot. An extended podule occupies two podule slots horizontally. A podule is a single or double width, standard depth eurocard with a 96 way DIN connector. The main computer PCB has a single 96 way DIN connector into which a four way backplane is attacted. This backplane decodes the individual physical slots so that each slot occupies a different address space while keeping the physical characteristics of all four slots the same. This allows a podule to be inserted into any podule slot without changing links.

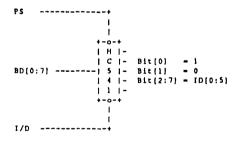

#### 9.14.2 Ilackplane

|         | +   |            | -+ |             |        |   |

|---------|-----|------------|----|-------------|--------|---|

|         | E I |            | 1  |             |        |   |

| S ( 6 ) | 01  | н          | 1  | Podule      | Select | 0 |

|         | 1   | С          | 1  | Podule      | Select | 1 |

| LA14    | a   | 1          | 1  | Podule      | Select | 2 |

| LA15    | 16  | з          | 1  | Podule      | Select | 3 |

|         | 1   | ,          | i  | • • • • • • |        | - |

|         |     | . <u>.</u> |    |             |        |   |

|         | •   |            | •  |             |        |   |

|         |     |            |    |             |        |   |

|         |     |            |    |             |        |   |

|         | *   |            |    |             |        |   |

|         |     |            |    |             |        |   |

|         |     |            | 1  |             |        |   |

| 1.721   | 01  | н          |    | Module      | Select | 0 |

|         | 1   | с          | 1  | Module      | Solect | 1 |

| 1.814   | 8   | 1          | 1  | Module      | Select | 2 |

| LA15    | 1b  | з          | 1  | Module      | Select | 3 |

|         | 1   | 9          | 1  |             |        |   |

|         | +   |            | -+ |             |        |   |

Note : delay on MS must meet IOAK setup and single N-cycle IOGT.

A 500 Hardware Guide Issue 0.0

## 9.15 Fan

Yes, we have one, and it is powered from SK12 or SK13.

## 9.16 RFI

The main PCB has a guard ring which is an isolated track on the inner ground plane made available at TP2-TP5 and FT5. All connector shells and RFI components should be connected to this ring which is start wired to the PSU. The idea is that this ring will carry less noise than the ground plane despite its higher inductance. In practise the A500 has no RFI components but allows experimentation.

## **10. Programming Details**

## 10.1 IOC Keyboard Asynchronous Receiver Transmitter (KART)

The KART provides an asynchronous serial link, to the keyboard- It is of fixed format with 8 bits to a character which is framed with one start bit and two stop bits. The least significant bit KD[0] is transmitted/received first. The KART divides into two halves, the receiver and the transmitter.

The ARM accesses the receiver via the *Serial Rx Data register*. A clock of 16 times the data rate is used by the KART to clock in the serial data from the KIN pin. When a data byte has been received, the SRx bit is asserted in the *IRQ Status B Register* to indicate that the byte is available for reading. False start bits of less than a half bit duration are ignored.

The ARM accesses the transmitter via the Serial Tx Data register. The byte written to the Serial Tx Data register is transmitted serially from the KOUT pin, and the STx bit is asserted in the IRQ Status B register to indicate that the transmission is finished and the Serial Tx Data register may be reloaded.

The receive and transmit speeds are the same and are programmed using counter 3.

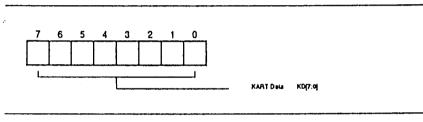

### 10.1.1 Serial Tx Data register

Figure 6: Serial Tx Data register 04H write

Writing to this register loads the serial output shift register, clean any outstanding TRx: interrupt and starts the transmission. An interrupt is raised when the register is ready to be reloaded.

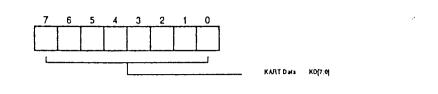

### 10.1.2 Serial Rx Data register

Reading from this register clears any outstanding SRx interrupt and returns the currently received byte. Data is only valid while the SRx bit is set in the *IRQ status B register*.

#### **10.1.3 Initialisation**

After Power-On, the KART is in an undefined state. The KART is initialised by programming the serial line speed using counter 3 and performing a read from the *Serial Rx Data register*, discarding the data byte. This will clear any outstanding receive interrupt and enable the KART for the next reception. Finally the *Tx Data register* should be written to. This will abort any transmission in progress, cause a new one to be started, and clear any STx interrupt.

A 500 Hardware Guide Issue 0-0

Figure 7: Serial Rx Data register 04H read

### **10.1.4 Receive Interrupt**

The SRx interrupt is set halfway though the reception of the last data bit. Care should be taken to ensure that the last bit has been received before the *Serial Rx data register* is read, to prevent this bit being interpreted as the start bit of the next packet.

Chapter 10

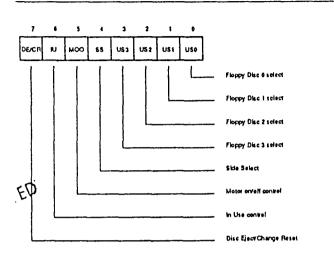

## 10.2 External Latch A

The Exsernal Latch A is a write only latch used to control parts of the floppy disc sub-system.

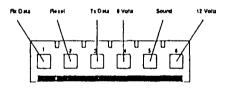

Figure 8: External Latch A 3360000H

### 10.2.1 Bit [0:3] US[0:3]

These bits select the floppy disc unit 0 through 3 when written LOW. Only one bit should be LOW at any one time.

#### 10.2.2 Bit 4 Side Select

This controls the side select line of the floppy disc interface.

- 0 =Side 1 upper

- 1 = Side 0 lower

#### 10.2.3 Bit 5 Floppy Motor ON/OFF Control

This bit controls the floppy disc motor line. Its exact use depends on the type of drive.

#### 10.2.4 Bit 6 In Use

This bit controls the INUSE line of the floppy disc. 1ts exact use depends on the type of drive.

A 500 Hardware Guide Issue 0-0

26

### 10.2.5 Bit 7 Disc Eject

This controls the DISC EJECT or DISC CHANGED RESET line of the floppy disc drive.

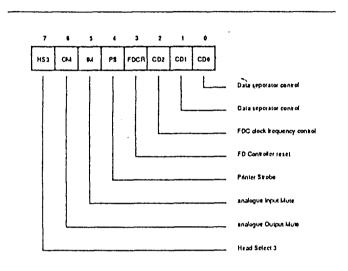

## **10.3 External Latch B**

The *External Latch B* is a write only register shared between several users who must maintain a consistent RAM copy. Updates must be made with 1RQ disabled.

Figure 9: External Latch B 3350018H

### 10-3.1 Bit [0:2] CD[0:2]

These bits control the Floppy disc data rate and format. The following settings are meaningful.

| ICC | 2 | 1 | : 0] | 1    | Function    |       | -1  | Name      | 01         | density | 1 | t/s        |

|-----|---|---|------|------|-------------|-------|-----|-----------|------------|---------|---|------------|

| !-  |   |   |      | .!   |             |       | -!  | !         | -!-        |         | ÷ |            |

| 1   | ٥ | ٥ | 0    | 1600 | rpm DD/300  | rpm   |     | SD        | ÷          | single  | 1 | DFS        |

| i.  |   |   |      |      | rpm \$D/300 |       |     |           | 1          | double  | I | ADFS/PCDOS |

| 1   | 1 | 1 | 0    | 1    | 300         | rmp : | SDI | 100       | 1          | beup    | ł | ογκ Ι      |

| 1_  |   |   |      |      |             |       | _1  | ۱ <u></u> | <u>ا</u> _ |         | 1 | I          |

Chapter 10

### 10.3.2Bit 3 FDCR

This controls the Floppy Disc Controler Reset Line. When programmed LOW the controller is RESET.

#### 10.3.3 Bit 4 Printer Strobe

This is used to indicate valid data on the printer outputs. It should be set HIGH when valid data has been written to the printer port and LOW after a typically  $5\mu$  seconds.

### 10.3.4 Bit 5 IMute

When set HIGH the analogue Input AIN is muted. When LOW AIN is mixed with the VIDC sound output and fed to the speaker.

#### 10.3.5 Bit 6 OMute

When set HIGH the analoge output AOUT is muted.

#### 10.3.6 Bit 7 HS3

This bit controls the HS3 line of the winchester disc interface. It allows extension of the ST506 interface to support upto 16 heads. It may be disabled by LK16 and LK17 to implement the standard ST506 "*Reduced Write Current*" function.

## **10.4 Interrupts**

The IO system generates two independent interrupt requests, IRQ and FIQ- Interrupt requests can be caused by events internal to IOC or by external events on the interrupt or control port input pins-

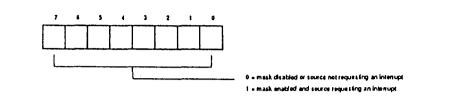

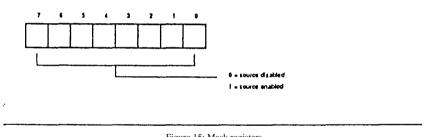

The interrupts are controlled by four types of register, status, mask, request and clear. The status registers reflect the current state of the various interrupt sources. The mask registers determine which sources may generate an interrupt. The request registers are the logical AND of the status and mask registers and indicate which sources are generating interrupt requests to the processor. The clear register allows clearing of interrupt requests where appropriate. The mask registers are undefined after power up.

The IRQ events are split into two sets of registers A and B. There is no priority encoding of the sources.

#### Internal Interrupt Events

- Timer interrupts TM[0:1].

- Power-on reset POR.

- Keyboard Rx data available SRx.

- Keyboard Tx data register empty STx.

- Force interrupts "I".

#### External Interrupt Events

- IRQ active low inputs IL[0:7] wired as PFIQ,SIRQ,SLCI,WIRQ,WDRQ,PIRQ,PBSY and RII.

- IRQ falling-edge input IF wired as PACK.

- IRO rising-edge input IR wired as VFLY.

- FIQ active high input FH[0:1] wired as FFIQ and FFDQ.

- FIQ active low input FL wired as EFIQ.

- Control port inputs C[3:5]

#### Level Interrupts

The majority of external and a few of the internal interrupt sources are level sensitive. When one of these sources has caused an interrupt it is cleared by removing the source.

#### Latched interrupts

The IF. IR. POR and TM[0:1] sources are latched. That is, once one of these sources has caused in interrupt, it must be cleared by an explicit write of "1" to the appropriate bit in the *IRQ Clear aA register*. One or many may be cleared in a single operation.

#### Synchronisation

All the interrupt sources are synchronised by the REF8M clock input. It can take up to three clock phases before a source is recognised as requesting an interrupt, and the same delay occurs between a level sensitive request going inactive at an input pin and the removal of the corresponding bit from the status register and the processor interrupt line.

## 10.5 IRQ Status A

Figure 10: IRQ Status A 3200010H read

#### 10.5.1 Bit 0 PBSY

This bit indicates that the printer is busy.

#### 10.5.2 Bit 1 RII

This bit indicates that a Ringing Indication has been detected by the serial line interface.

#### 10.5.3 Bit 2 Printer Acknowledge

This bit indicates that a printer acknowledge pulse has been received.

#### 10.5.4 Bit 3 Vertical flyback

This bit indicates that a vertical flyback has commenced.

#### 10.5.5 Bit 4 Power-on Reset

This bit indicates that a power-on reset has occurred.

#### 10.5.6 Bit [5:6] Timer 0 and Timer 1 events

These bits indicate that timer events have occurred.

Note : latched interrupt.

#### 10.5.7 Bit 7 Force

This hit is used to force an IRQ request. It is usually owned by the FIQ owner and is used to downgrade FIQ requests into IRQs.

Programming Details

## 10.6 IRQ Status B

Figure 11: IRQ Status 3200020H read

#### 10.6.1 Bit 0 Podule FIQ request

This bit indicates that a podule FIQ request has been received. It should usually be masked OFF.

#### 10.6.2 Bit 1 Sound buffer swap

This bit indicated that the MEMC sound buffer pointer has been reloaded.

#### 10.6.3 Bit 2 Serial line controller

This bit indicates that a 65C51 serial line controller interrupt has occured.

#### 10.6.4 Bit 3 Winchester Interrupt

This bit indicates that a Winchester interrupt has occured.

#### 10.6.5 Bit 4 Winchester data request

This bit indicates that a Winchester data request has occured.

#### 10.6.6 Bit 5 Podule Interrupt request

This bit indicates that a Podule IRQ request has occured.

#### 10.6.7 Bit 6 Keyboard transmission event

This bit indicates that the keyboard transmit register is empty and may be reloaded.

#### 10.6.8 Bit 7 Keyboard reception event

This bit indicates that the keyboard reception register is full and may be read..

## **10.7 Interrupt Status FIQ**

Figure 12: Interrupt Status FIQ 3200030H read

#### 10.7.1 Bit 0 floppy disc data request

This bit indicates that a Floppy Disc Data Request has occured.

#### 10.7.2 Bit 1 Floppy disc Interrupt request

This bit indicates that a Floppy Disc Interrupt Request has occured.

#### 10.7.3 Bit 2 ECOnet Interrupt request

This bit indicates that a ECOnet Interrupt Request has occured.

#### 10.7.4 Bit [3:5] Undefined

See IOC data sheet for details.

#### 10.7.5 Bit 6 Podule FlQ request

This bit indicates that a podule FIQ Request has occured.

#### 10.7.6 Bit 7 Force

This bit allows an FIQ interrupt request to be generated.

## 10.8 IRQ Clear register

Figure 13: IRQ Clear register 14H write

## 10.9 Interrupt Request registers 3200014H 3200024H 3200034H read

These registers show which interrupt sources are currently enabled and active. They give the logical AND of the corresponding *status and mask* registers.

| (i) IRQ request A  | address 32000141H |

|--------------------|-------------------|

| (ii) IRQ request B | address 32000241H |

| (iii) FIQ request  | address 32000341H |

Figure 14: Request registers

## 10.10 Interrupt Mask registers 3200018H 3200028H 3200038H read/write

The mask registers are readable to simplify the sharing of these registers between a number of interrupt handlers.

- (i) IRQ mask A address 3200018H

- (ii) IRQ mask B address 3200028H

- (iii) FIQ mask address 3200038H

## **10.11 Control Port**

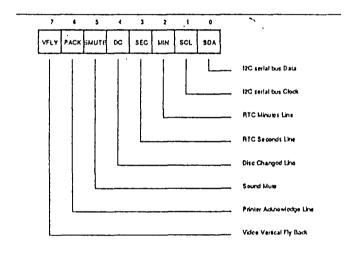

The *control register* allows the external control pins C[0:5] to be read and written and the status of the PACK and VFLY inputs to be inspected. The C[0:5] bits manipulate the C[0:5] IO Port. When read, they reflect the current state of these pins. When written LOW the output pin is driven LOW. These outputs are open-drain, and if programmed HIGH the pin is undriven and may be treated as an input.

On reset all bits in the control register are set to "1".

#### 10.11.1 C[0:1) The I2C

The C[0:1] pins are used to implement the bi-directional serial I2C bus to which the Real Time Clock and battery RAM are connected. For further details see PCF8570 and PCF8573 data sheets.

#### 10.11.2 Control port read

Figure 16: Control port 3200000H read

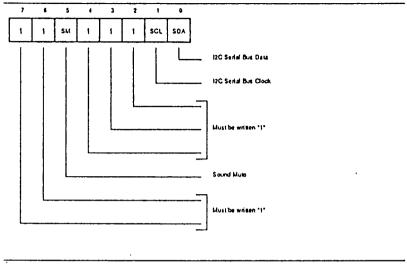

#### 10.11.3 Control port write

C[6:7] control internal test modes and if programmed to 0 will cause the counters and KART to malfunction.

In the A500 C[2:4] are wired as inputs and if these bits are programmed to 0 they will become outputs causing excessive current to be draw by the chip.

Figure 17: Control port 3200000H write

## **10.12** Counters

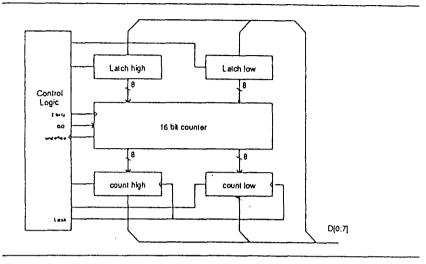

Four identical 16 bit counters are provided. Two are used as timers, the third for the keyboard BAUD rate and the fourth as a general purpose output. They all have fully programmable start/reload values.

Each counter consists of a 16 bit down counter, a 16 bit input latch (*latch low* and *latch high*) and a 16 bit output latch (*count low* and *count high*) which contains the value of the counter when the *latch command* is given. The counter decrements continuously, clocked at 2 MHz. When it decrements to zero, it is reloaded from the *input latch* and recommences decrementing. The reload is used to trigger different events depending on the use of the counter. If a counter is loaded with zero it continuously reloads and does not count. If the *GO register* is written at the same time as the counter reloads an extra 2 MHz clock tick is taken o reload. After power-on the state of the counters is unknown.

latch = latch low + 256 \* latch high

#### 10.12.1 Register actions

| Latch low     | Writing to this updates the low order byte of the input latch                       |

|---------------|-------------------------------------------------------------------------------------|

| Latch high    | Writing to this updates the high order byte of the input latch                      |

| GO command    | Writing to this causes the counter to be reloaded immediately with the latch value. |

| Count low     | This causes the low order byte of the output latch to be read.                      |

| Count high    | This causes the high order byte of the output latch to be read.                     |

| Latch command | This causes the current value of the counter to be placed in the output latch.      |

#### 10.12.2 Counter schematic

Figure 13: Counter schematic

#### **10.12.3 Counter Registers**

|               |             | Addre | SS  |     |         |

|---------------|-------------|-------|-----|-----|---------|

|               | for counter |       |     |     | read or |

|               | 0           | 1     | 2   | 3   | write   |

| Latch low     | 40H         | 50H   | 60H | 70H | write   |

| Latch high    | 44H         | 54H   | 64H | 74H | write   |

| GO command    | 48H         | 58H   | 68H | 78H | write   |

| Count low     | 40H         | 50H   | 60H | 70H | read    |

| Count high    | 44H         | 54H   | 64H | 74H | read    |

| Latch command | 4CH         | 50H   | 6CH | 7CH | write   |

#### 10.12.4 Counters 0 and 1

Two general purpose timers are provided. The reload event sets a timer interrupt, TM[0:1] in the *IRQ status A register*. The interrupt is cleared via the *IRQ Clear A register*. In order to generate an interrupt after time  $T_{interval}$  the 16 bit value, (*latch*), to be used is calculated from the following equation.

$$T_{interval} = latch/2 \ \mu seconds$$

#### 10.12.5 Counter 2 (BAUD)

The counter 2 output is used to drive the BAUD pin. The reload event toggles the BAUD clock line. In order to generate a clock of frequency  $f_{BAUD}$ , the 16 bit value, (*latch*), to be used is calculated from the following equation.

$f_{BAUD} = 1/(latch+1) MHz$

The maximum BAUD rate of 500kHz is obtained by programming *latch* = 1.

#### 10.12.6 Counter 3 (KART)

The counter 3 output controls the speed of the keyboard serial link. In order to generate a baud rate  $k_{BAUD}$  the 16 bit value, (*latch*), to be used is calculated from the following equation.

$k_{BAUD} = 1/((latch+1)*16) MHz$

The maximum baud rate of 31250Hz is obtained by programming *latch=1*.

# 11. Reset and Power-on

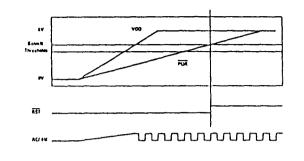

The A500 may be reset in two ways: by driving the bidirectional RST line LOW, or by driving the POR line LOW. The RST line in connected to the reset switch on the back right of the keyboard. Pressing this will reset both the keyboard and the A500. The POR pin is connected to an RC network to ensure that when power is first applied to the A500, a system reset signal is generated on RST.

POR causes an internal latched interrupt to be set to allow system software to differentiate between "power-on" and "soft" resets, and ensures that peripheral chips have had a stable clock for a suitable length of time before being released from reset. The keyboard may be unplugged and replugged without reseting the A500 as it contains its own power-on reset circuit. The control register is initialised on reset causing the C[0:5] pins to be set to a known state, before the processor commences execution.

Figure 19: A 500 power-on reset circuit

Figure 20: Power-on timing

# 12. Mechanical

# A500 Back Panel

- **12.1** Construction

- **12.2 Installing Podules**

- 12.3 The Disc Tray

- 12.4 Removing the Main PCB

- **12.5 Changing the flatteries**

- 12.6 Changing the ROM's

- 12.7 Air flow

# 13. Main PCB Connectors, Links and Test Points

## 13.1 TP1 HLD Head Load

This test point makes the HDC head load output available.

## 13.2 TP2-TP5 Guard rail

These test points make the GUARD rail available.

## 13.3 SK1 Audio Output

This connector provides STEREO audio output.

## 13.4 SK2 RGB Video output

This connector provides the RGB and sync outputs.

## 13.5 SK3 Monochrome video output

This connecter provides Monochrome Video.

## 13.6 SK4 RS423 Serial line

This plug ptovides an "AT" serial line interface to the RS423 standard.

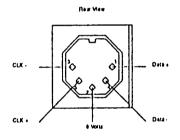

Serial SK4 Rear View DCD TxD DTR RxD 0 Volts 2 ĥ f. h 77 7 8 6 1 RI DSR RTS CTS

## 13.7 SK5 Parallel printer connector

This connector provides a parallel printer interface.

| Pin | Function   | Pin | Function |

|-----|------------|-----|----------|

| 1   | STB        | 14  | 0V       |

| 2   | ov         | 15  | D6       |

| 3   | D <b>0</b> | 16  | 0V       |

| 4   | ov         | 17  | D7       |

| 5   | D1         | 18  | ov       |

| 6   | 0V         | 19  | УСК      |

| 7   | D2         | 20  | 0V       |

| 8   | 0V         | 21  | BSY      |

| 3   | D3         | 22  | 07       |

| 10  | ov         | 23  | n/c      |

| 11  | D4         | 24  | ov       |

| 12  | 0V         | 25  | n/c      |

| 13  | D5         | 26  | n/c      |

## 13.8 SK6 Podule backplane expansion

This connect may be used to attatch one PODULE or the expansion backplane.

| Pin | 8        | b     | c (Backplane) | c (Podule) |

|-----|----------|-------|---------------|------------|

| 32  | V 5      | 0[31] | V12           | V12        |

| 31  | BD[0]    |       | CLKSYS        | CLKSYS     |

| 30  | BD[1]    |       | V 5           | V 5        |

| 29  | BD[2]    |       | REF8M         | REF8M      |

| 28  | BD(3)    |       | CLKS          | CLK8       |

| 27  | BD[4]    |       | CLK2          | CLK2       |

| 26  | BD ( 5 ) |       |               |            |

| 25  | BD[6]    |       | BL            | BL         |

| 24  | BD[7]    |       | NIOAK         | NIOVK      |

| 23  | BD[8]    |       | NIOGT         | NIOGT      |

| 22  | 00(9)    |       | S[6]          | PS         |

| 21  | BD[10]   |       | S[7]          | s(7)       |

| 20  | BD[11]   | •     | C0            | С0         |

| 19  | BD(12)   |       | ci 🗅          | C1         |

| 18  | BD(13)   |       | EFIQ          | EFIQ       |

| 17  | BD(14)   | •     | NPFIQ         | NPFIQ      |

| 16  | BD(15)   | •     | NPIRQ         | NP 1 RQ    |

| 15  | LA[2]    |       | NPRE          | NPRE       |

| 14  | LA[3]    |       | NPWE          | NPWE       |

| 13  | LA[4]    | •     | LRNW          | LRNW       |

| 12  | LA[5]    |       | NRST          | NRST       |

| 11  | LA ( 6 ) | •     | PHILB         | PHIIB      |

| 10  | LA[7]    | •     | OPC           | OPC        |

| ,   | LA[8]    |       | CPI           | CPI        |

| 8   | LA[9]    | •     | CPB           | CPB        |

| 7   | LA[10]   | •     | CPA           | CPA        |

| 6   | LA[11]   | •     | LA[21]        | MS         |

| 5   | LA[12]   | •     | AGND          | AGND       |

| 4   | LA[13]   | •     | LOUT          | AOUT       |

| 3   | LX(14)   |       | AIN           | AIN        |

| 2   | LA[15]   | •     | V-5           | V-5        |

| 1   | V0       | D[00] | VO            | VO         |

## 13.9 SK7 Floppy disc drive conRector

This socket is used to connect o the FD. Power may be supplied via this cable or seperately. See LK14 and LK15.

| Pin | Function   | Pin | Function   |

|-----|------------|-----|------------|

| 1   | disc eject | 18  | DIR        |

| 2   | n/c        | 19  | 0V         |

| 3   | 5V or 0V   | 20  | STEP       |

| 4   | in use     | 21  | 0V         |

| 5   | 5V or OV   | 22  | Write Data |

| 6   | SEL 3      | 23  | 0V         |

| 7   | 5V or OV   | 24  | Write Gate |

| 8   | index      | 25  | 07         |

| 9   | 5V or OV   | 26  | Track 00   |

| 10  | SEL O      | 27  | 0V         |

| 11  | 5V or OV   | 28  | Write Prot |

| 12  | SEL 1      | 29  | 12V or OV  |

| 13  | 0V         | 30  | Read Data  |

| 14  | SEL 2      | 31  | 12V or OV  |

| 15  | 0V         | 32  | Side Sel   |

| 16  | Motor On   | 33  | 12V or OV  |

| 17  | 0V         | 34  | Ready      |

## 13.10 SK8 and SK9 Winchester data connector

These two connector are used to attatch the winchester disc drives.

```

SK8 for DRIVE 0

SK9 for DRIVE 1

Pin

Function

13

Write Data +

14

Write Data -

17

Read Data +

18

Read Data -

2,4,6,8,11,12,15,16,19,20

0 Volts

1,3,5,7,9,10

n/c

```

## 13.11 SK10 Winchester control connector

This connecor is used for the daisy chain winchester control cable.

| Pin | Function   | Pin | Function |

|-----|------------|-----|----------|

| 1   | 0V         | 18  | HSELI    |

| 2   | RWC or HS3 | 19  | 0V       |